contents: 0-1. CA Intro

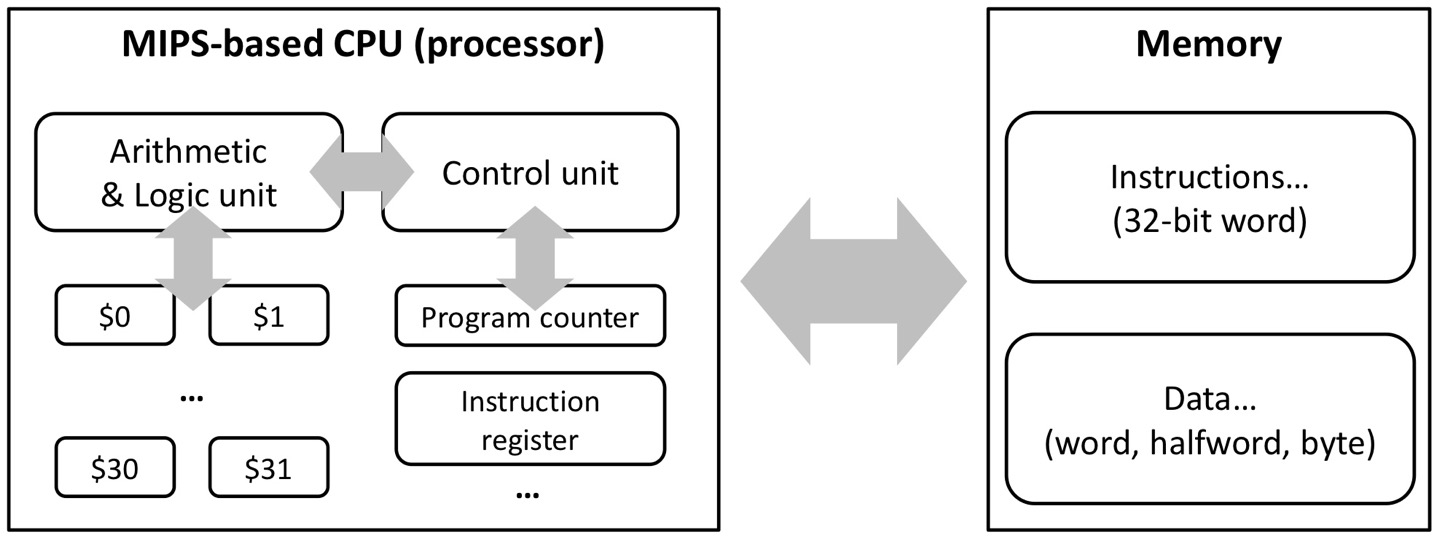

Common HW design for MIPS ISA

CPU, register, and memory

- Control unit (CU) directs the operation of the processor

- Arithmetic & logic unit (ALU) does the operation

$0, ..., $31hold the value that will be used in the operation (called general purpose register)- Program counter (PC) contains the memory address of the instruction will be executed

- Instruction register (IR) contains the current instruction

Execution of the instruction

- Step 1 (fetch): CU says "load the instruction from the memory address in PC to IR"

- Step 2 (decode): CU says "the instruction stored in IR means

ADD $s0, $s1, $s2 - Step 2 (execute): ALU does the add operation with the values in

$s1and$s2and stores the computation result in$s0

Operation

Arithmetic operations

Instructions for arithmetic

| Operation | C | Java | MIPS assembly language | Example |

|---|---|---|---|---|

| Add | + | + | add (R), addi (I) |

add $t0, $t1, $t2 |

| Subtract | - | - | sub (R) |

sub $t0, $t1, $t2 |

Logical operations

Instructions for bitwise manipulation

| Operation | C | Java | MIPS assembly language | Example |

|---|---|---|---|---|

| Bitwise AND | & | & | and(R), andi(I) |

and $t0, $t1, $t2 |

| Bitwise OR | | | | | or (R), ori(I) |

or $t0, $t1, $t2 |

| Bitwise NOR | ~ | ~ | nor(R) |

nor $t0, $t1, $t2 |

MIPS has no NOT instruction Instead, it has NOR R-type instruction

- a NOR b == NOT (a OR b)

- But, we can do the NOT operation with NOR:

nor $t0, $t1, $zero!

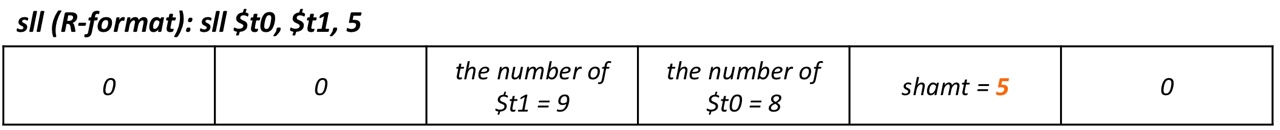

Shift operations

| Operation | C | Java | MIPS assembly language | Example |

|---|---|---|---|---|

| Shift left | << | <<< | sll (R) |

sll $s1, $s2, 10 ($s1 = $s2 << 10) |

| Shift right | >> | >>> | srl (R) |

srl $s1, $s2, 10 ($s1 = $s2 >> 10) |

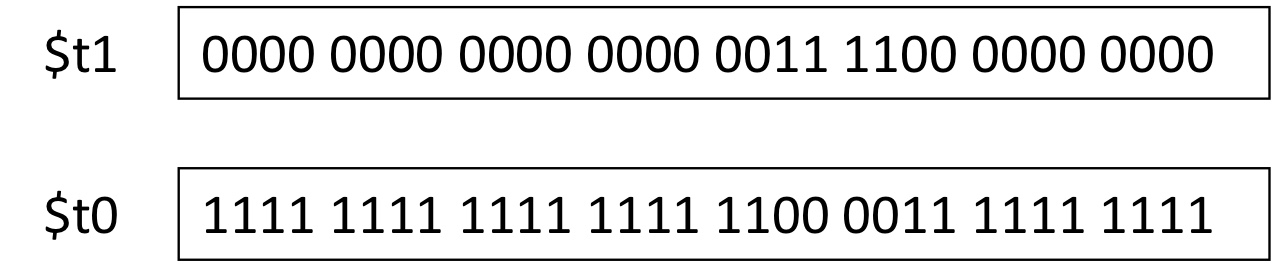

- shamt: how many positions to shift

- Shift left/right logical (sll / srl)

- Shift left/right and fill with 0 bits

- (unsigned only) sll with i bits = multiply by

- (unsigned only) srl with i bits = divide by

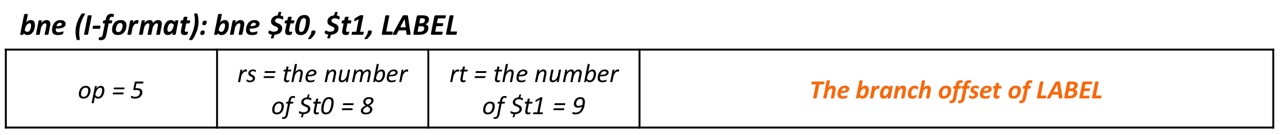

Conditional operations

| Operation | MIPS assembly language | Example |

|---|---|---|

| Conditional branch | beq(I) |

beq $t0, $t1, LABEL (if t1, goto LABEL) |

bne(I) |

bne $t0, $t1, LABEL (if t1, goto LABEL) |

|

| Unconditional branch | j(I) |

j LABEL (goto LABEL) |

Instructions for making decisions Usually combined with goto statements and labels there are no branch instructions like blt (less than) and bge (greater than or equal to)

Why?

- Handling <, >, <=, >=, ... is slower and more complicate than =, !=

- It will cause increase of instruction count and clock period or CPI

Instead, MIPS provides others

| operation | MIPS assembly language | Example |

|---|---|---|

| Set on less than | slt(R), slti(I) | slt t1, t1 < t0 = 1; else $t0 = 0) |

slt is used in combination with beq and bne

slt $t0, $t1, $t2

bne $t0, $zero, LABEL

beq $t0, $zero, LABEL