contents: 0-1. CA Intro

MIPS ISA

What is MIPS ISA

- Microprocessor without Interlocked Pipelined Stages

- A kind of ISA

Design principles

- Simplicity favors regularity

- Smaller is faster

- Make the common case fast

Design Principle 1

Simplicity favors regularity

- Regularity: all MIPS arithmetic instructions include a single operation & three operands

- Regularity makes implementation simpler

- Simplicity enables higher performance at lower cost

Examples

- add a, b, c

- sub a, a, d

Design Principle 2

Smaller is faster

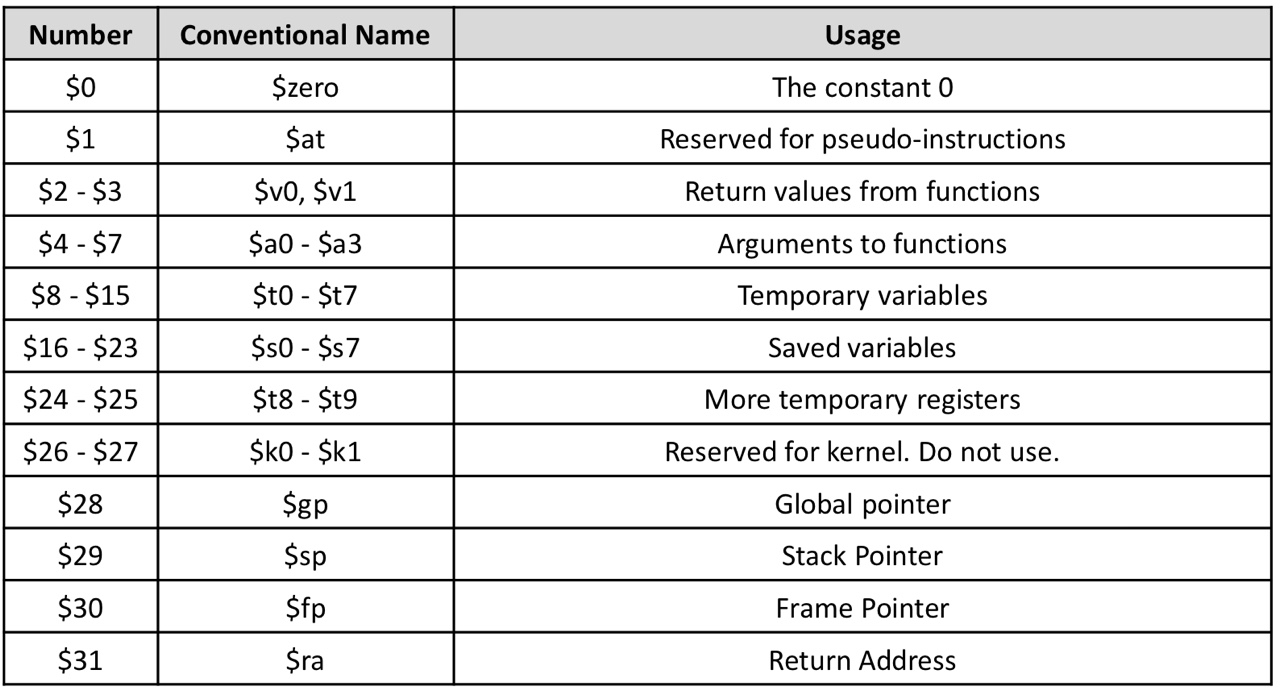

- Operands of MIPS arithmetic instructions must be chosen in a small number of registers

- Register: Fast locations for data

- 32 32-bit registers in MIPS

- 32 is that can be represented by using 5 bits

Practice 1

C code:

f = (g + h) - (i + j)Compiled MIPS assembly language code:

add $t0, $s1, $s2

add $t1, $s3, $s4

sub $s0, $t0, $t1Memory instruction

Memory organization

keep a small amount data in registers and other remaining, complex data in memory

- Load values from memory into registers

- Store results from registers to memory

Address

A memory address is an index to the memory array, starting at 0 MIPS uses byte addressing (Each address identifies an 8-bit byte)

But, most data items are larger than a byte. So, they use "words"

- In MIPS, a ward is 32 bits

- Registers also hold 32-bit of data

Alignment restrictions

- The start address of each data should be multiple of N, where N is the size of the data

- In MIPS, words must start at a addresses that are multiples of 4

- Some data items use one or two bytes (halfword)

Byte ordering

- Big endian(MIPS): place the most significant byte first and the least significant byte last

- Little endian: place the least significant byte first and the most significant byte last

Load/Store

- lw reg1 offset(reg2): Load 32-bit word from the memory address reg2 + offset into reg1

- sw reg1 offset(reg2): Store 32-bit word in reg1 at the memory address reg2 + offset

- lh/sh and lb/sb instructions load/store halfwords and 8-bit of data

Practice 2

C code:

g = h + A[8]- A is an array of 4-bytes words

- The value of g and h are in

$s1and$s2 - The base address of A is in

$s3

Compiled MIPS assembly language code:

lw $t0, 32($s3)

add $s1, $s2, $t0Practice 2

C code:

A[12] = h+ A[8]- A is an array of 4-bytes words

- The value of h is in

$s2 - The base address of A is in

$s3

Compiled MIPS assembly language code:

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)Practice 3

C code:

f = (g + h) - (i + j)- f, g, and h are in

$s0,$s1, and$2respectively - Halfwords i and j are sequentially stored in memory

- The start address of i is stored in

$s3

Compiled MIPS assembly language code:

add $t0, $s1, $s2

lh $t1, 0($s3)

lh $t2, 2($s3)

add $t3, $t1, $t2

sub $s2, $t0, $t3Design Principle 3

Make the common case fast

Common case : a program uses a small constant in an operation many times

Solution: support

-

16-bit immediate operands for handling the constants

- no need to access memory to load the constants

addi $t0, $t0, 4: addi is an add immediate instruction

-

MIPS register 0 (

$zero) contains the constant 0add $t0, $t1, $zero: move values between two registers$t0andt1

Practice 4

C code:

f = A[10] - i + 4Ais an array of bytes and its base address is stored in$s0fandiare stored in$s1and$s2respectively

Compiled MIPS assembly language code:

lb $t0, 10($s0)

sub $t1, $t0, $s2

addi $s1, $t1, 4Summary: MIPS ISA

Key underlying design principles

- Design principle 1. Simplicity favors regularity

- All MIPS arithmetic instructions include a single operation & three operands

- Design principle 2. Smaller is faster

- Operands of MIPS arithmetic instructions must be chosen in a small number of registers

- MIPS keeps more complex data in memory and supports data transfer between memory and registers

- Design principle 3. Make the common case faster

- Support 16-bit immediate operands for handling small constants +

$zero

- Support 16-bit immediate operands for handling small constants +